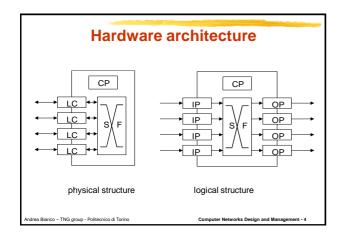

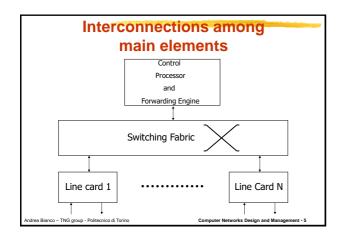

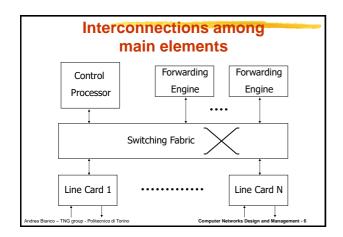

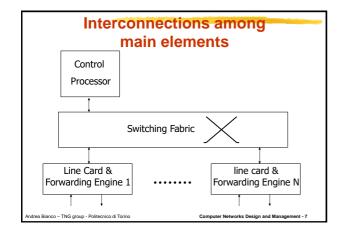

#### Hardware architecture: main elements

- Line cards

- support input/output processing and <code>rx/tx</code>

- store packets in queues

- adapt packets to the internal format of the switching fabric

Comp

er Networks Design and Manag

- support data link protocols

- classify packets

- schedule packets

- support security

- · Switching fabric

Bianco – TNG group - Politecnico di Torino

- transfers packets from input ports to output ports

#### Hardware architecture: main elements

- · Control processor/network processor

- runs routing protocols

- computes routing tables

- manages the overall system

#### · Forwarding engines

ea Bianco – TNG group - Politecnico di Torino

- compute the packet destination (lookup)

- inspect packet headers

- rewrite packet headers

Computer Networks Design and M

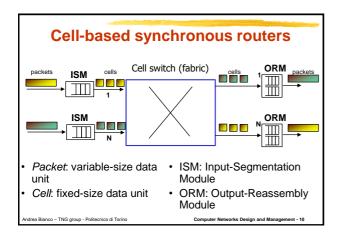

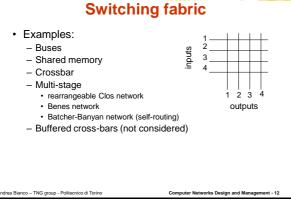

### Switching fabric

- · Our assumptions:

- Bufferless

- to reduce internal hardware complexity

- Non-blocking

a Bianco – TNG group - Politecnico di Torino

• it is always possible to transfer in parallel from input to output ports any non-conflicting set of cells

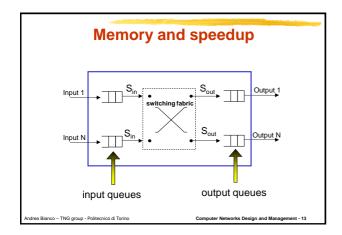

#### Speedup

- The speedup (increase in speed with respect to line speed) determines switch performance:

- S<sub>in</sub> = reading speed from input queues

- $-S_{out} =$  writing speed to output queues

- The speedup is also a technological constraint

- Maximum speedup factor:

$-S = max(S_{in}, S_{out})$

Bianco – TNG group - Politecnico di Torino

#### **Faster and faster**

- · Need for high performance routers

- to accommodate the bandwidth demands for new users and new services

- to support QoS

- to reduce costs

a Bianco – TNG group - Politecnico di Torino

- Moore's law (electronic packet processing power) is too slow with respect to the increase in link speed

- · The bottleneck is memory speed

Computer Networks Design and Management

#### Single packet processing

- The time to process one packet is becoming shorter and shorter

- Worst case: 40-Byte packets (ACKs)

- 3.2 μs at 100 Mbps

- 320 ns at 1 Gps

- 32 ns at 10 Gps

- 3.2 ns at 100 Gbps

- 320 ps at 1Tbps

aa Bianco – TNG group - Politecnico di Torino

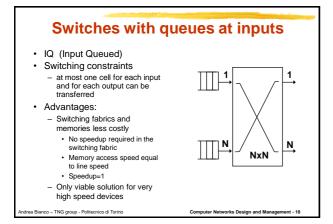

#### Switches with queues at outputs

Co

- OQ (Output Queued)

- The switching fabric is able to transfer to any output all cells received in one time slot

- 100% throughput

aa Bianco – TNG group - Politecnico di Torino

- Optimal average delay

- Speedup N with respect to line speed is required in switching fabric speed and in output port memory access

works Design and Mana

Computer Networks Design and Manag

ant - 16

Computer Ne

tworks Design and Ma

a Bianco – TNG group - Politecnico di Torino

Pag. 7

Pag. 8

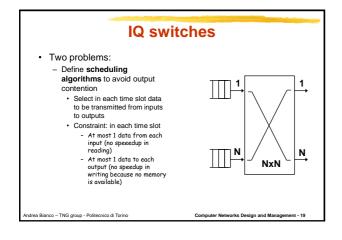

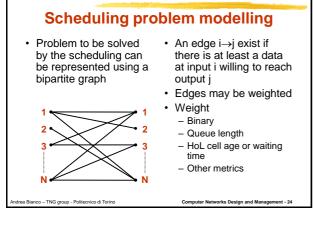

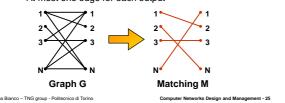

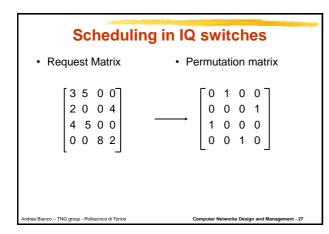

- time slot, a matching over the bipartite graphs.

- Select at most N edges with constraints

At most one edge for each input

- At most one edge for each input

At most one edge for each output

####

#### **Traffic description**

- A<sub>ii</sub>(n) = 1 if a packet arrives at time n at input i, with destination reachable through output j

- $\lambda_{ii} = E[A_{ii}(n)]$

- · An arrival process is admissible if:

- $-\sum_{i} \lambda_{ii} < 1$

$-\sum_{j}\lambda_{ij} < 1$

- · no input and no output are overloaded on average

- OQ switches exhibit finite delays (for admissible traffic)

Computer Networks Design and Manag

Computer Networks Design and Mana

Traffic matrix:  $\Lambda = [\lambda_{ij}]$

a Bianco – TNG group - Politecnico di Torino

#### Scheduling policies: objective

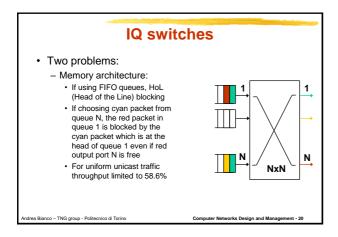

- · Let us consider a NxN IQ

- Denote by *i* the input port index and by *j* the output port • index

- Goal: assuming infinite buffer size, transfer any admissible traffic pattern with no losses

- · Solutions are known

- If traffic pattern is known in advance

- TDM of Birkhoff von Neumann algorithm

For admissible unknown traffic patter

- Maximum Weight Matching

Maximum Size Matching

- · Several heuristics are proposed for unknown traffic pattern

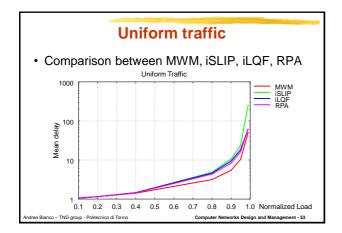

- iSLIP, iLQF, iOCF, 2DRR (WFA), MUCS, RPA, and many others

a Bianco – TNG group - Politecnico di Torino

nco – TNG group - Politecnico di Torino

#### **Birkhoff - von Neumann theorem**

Any doubly stochastic matrix Λ can be expressed as convex combination of permutation matrices π<sub>n</sub>:

$$\Lambda = \sum_{n} a_{n} \pi_{n}$$

• with \_\_a\_≥0

$-\sum_{n} a_{n} = 1$

drea Bianco – TNG group - Politecnico di Torino

Bianco – TNG group - Politecnico di Torino

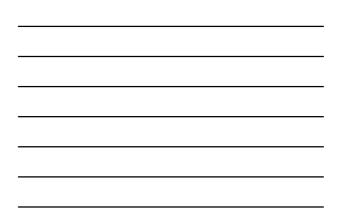

## Scheduling non-uniform known traffic

Computer Networks Design and Mana

- Thanks to the Birkhoff von Neumann theorem

- If the traffic is known and admissible, 100% throughput can be achieved by a TDM scheme using:

- for a fraction of time  $a_1$  matching  $M_1$  ( $\pi_1$ )

- for a fraction of time  $a_2$  matching  $M_2$  ( $\pi_2$ )

- for a fraction of time  $a_k$  matching  $M_k$  ( $\pi_\kappa$ )

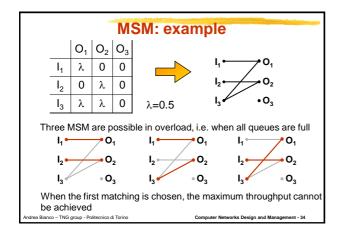

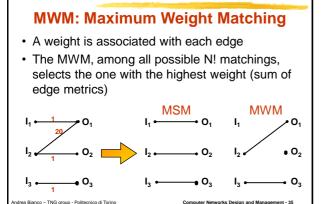

#### **MSM: Maximum Size Matching**

- MSM maximizes the number of data transferred in a single time slot, i.e. select the maximum number of edges

- Instantaneous throughput maximization.

- Asymptotic computational complexity is  $O(N^{2.5})$

- Non optimal algorithm

ea Bianco – TNG group - Politecnico di Torino

Some admissible traffic pattern cannot be scheduled, i.e. it does not always achieve 100% throughput.

Computer Networks Design and Management - 33

works Design and Manag

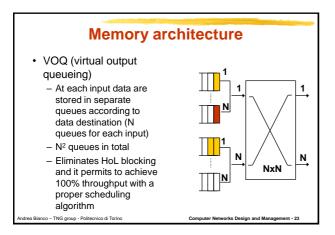

### **MWM: Maximum Weight Matching**

- MWM does not maximize instantaneous throughput (worse than MSM)

- It was demonstrated that a MWM algorithm

- in IQ switches with VOQ architecture

- under admissible trafficwith infinite queue size

- with infinite queue siz

- when using as weight either the queue length or the age of the HoL data

achieves100% throughput

- Asymptotic computational complexity O(N<sup>3</sup>)

- With finite queue size, it behaves similarly to MSM

- Problems with delays and possible starvation

Andrea Bianco – TNG group - Politecnico di Torino

Computer Networks Design and Management - 36

#### **Practical solutions**

- · Need to define heuristics

- with reasonable complexity

- that can be implemented in hardware

- · Any scheduling algorithm defines three aspects:

- A method to compute the weights to be associated with each edge (metric):

- Approximate MSM

- Binary (queue occupancy)

- Approximate MWM

- Queue length (it is an indication of the fact that the queue, which is associated with an input/output pair, is suffering)

- Age of HoL data

- Interface load

- Ad hoc metrics to select critical edges/nodes

#### **Practical solutions**

- ...

anco – TNG group - Poli

- A heuristic algorithm to determine a matching

- A contention resolution algorithm among edges with the same metric:

- round-robin (initial choice state dependent)

- sequential search (initial choice non state dependent)

- random

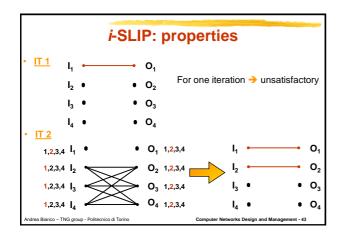

#### *i*-SLIP

• Iterative algorithm

ea Bianco – TNG group - Politecnico di Torino

- It defines a heuristic algorithm which determines, with a proper number of iterations, a *maximal size* matching (i.e., a matching that cannot be further extended with other edges selection)

- · Metric is the queue occupancy

- To solve contentions, it exploits an arbiter for each input and for each output

tworks Design and N

## Router/switch architectures

#### *i*-SLIP

- In each iteration, three phases can be identified:

- Request: each unmatched input sends a request to every output for which it has a cell

- Grant: each unmatched output that has received requests, sends a grant to one of the requesting inputs.

- Contentions solved by a round robin mechanism.

- Accept: if an unmatched input receives grants, it selects an output and becomes matched to it

Contentions solved by a round robin mechanism

Computer Networks Design and Mana

ndrea Bianco – TNG group - Politecnico di Torino

- TNG group - Politecnico di Torino

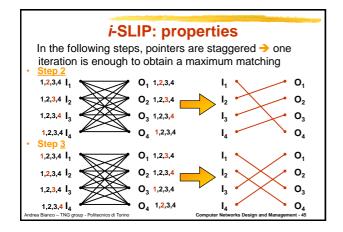

#### i-SLIP: counters

- Each input (output) has a pointer associated with to solve contentions

- The output pointer is incremented, modulo N, by one unit beyond the index of the input to which the grant was issued

- The input pointer is incremented, modulo N, by one unit beyond the index of the output from which an accept was received

## Router/switch architectures

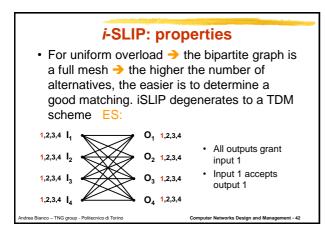

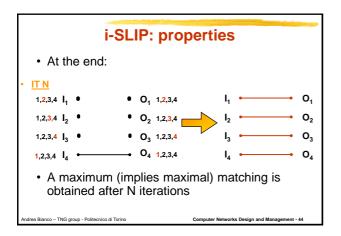

#### *i*-SLIP: properties

- Each iteration has a computational complexity of O(N<sup>2</sup>), but it can be easily made parallel

- · Worst case in one iteration: 1 edge is selected

- When executing N iterations, the matching is maximal (depends on the choice made but cannot be extended)  $\rightarrow$  however, the computational complexity is  $O(N^3)$

- Experimental results show that log<sub>2</sub>N iterations are in general enough to obtain good performance

- · Performance drops if pointers are badly synchronized

- iSLIP was implemented on a single chip in the Cisco 12000 router

Computer Networks Design and Mar

a Bianco – TNG group - Politecnico di Torino

#### **iSLIP:** extensions

· Use the same heuristic algorithm (3-phase) but with different metrics / QF

*i*OCF

- Queue length

- HoL cell age

co – TNG group - Politecnico di Torino

- · Input send requests containing the weight

- Contentions are solved using the weight first, only for equal weights the choice is random

- Does not exploit pointer synchronization to obtain good performance, rather the edge weight

- OCF has better delay properties (never starves data), but the increase in complexity is significant and makes the algorithm practically unfeasible

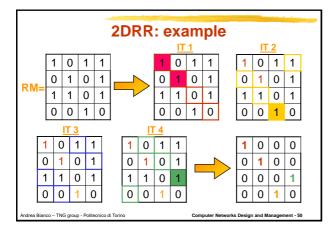

2DRR: Two Dimensional **Round Robin**

- · Operates on the request matrix

- · Extension of the WFA (Wave Front Arbiter), very easily implementable in hardware

- · Definitions

- Generalized diagonal is a set of N elements of a matrix NxN such that two elements do not belong to the same row or column

- A set of N diagonal is said to be covering if each element of the matrix belongs to one and only one diagonal

- In each time slot, the algorithm goes through N iterations

Bianco – TNG group - Polite

#### 2DRR: Two Dimensional Round Robin

- At the beginning, all links (input-output connections) are enabled

- At each iteration, a given generalized diagonal is chosen

- Only enabled links may be selected if the are covered by the elements belonging to the chosen diagonal

- If a link from input i to output j is selected, all requests issued by i or sent to j are disabled for the current time slot (cannot be chosen in the matching)

- In N iterations, all N generalized diagonal are considered and the request matrix is fully covered

Computer Networks Design and Mana

aa Bianco – TNG group - Politecnico di Torino

#### 2DRR: Two Dimensional Round Robin

- At each time slot, a different covering set of generalized diagonal is chosen, to improve fairness

- Indeed, edges covered to the first diagonal chosen are more likely selected

- Round robin over different sets of covering diagonal and round robin on each element in the set

- · Emulates a MSM

- · Not easy to extend to other metrics

- Asymptotic computational complexity O(N<sup>2</sup>)

Andrea Bianco – TNG group - Politecnico di Torino

puter Networks Design and Management - 51

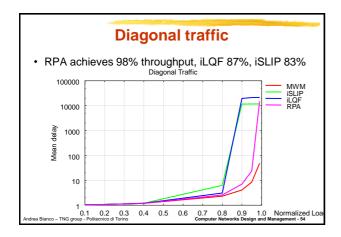

| Traffic scenarios                                                                                                                                                   |                                                                                                                           |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|

| <ul> <li>Uniform traffic         <ul> <li>Bernoulli i.i.d. arrivals</li> <li>usual testbed in the<br/>literature</li> <li>"easy to schedule"</li> </ul> </li> </ul> | $\Lambda = \frac{\rho}{N} \begin{bmatrix} 1 & 1 & 1 & 1 \\ 1 & 1 & 1 & 1 \\ 1 & 1 &$                                      |  |  |  |

| <ul> <li>Diagonal traffic         <ul> <li>Bernoulli i.i.d arrivals</li> <li>critical to schedule, since<br/>only two matchings are<br/>good</li> </ul> </li> </ul> | $\Lambda = \frac{\rho}{3} \begin{bmatrix} 2 & 1 & 0 & 0 \\ 0 & 2 & 1 & 0 \\ 0 & 0 & 2 & 1 \\ 1 & 0 & 0 & 2 \end{bmatrix}$ |  |  |  |

| Andrea Bianco – TNG group - Politecnico di Torino                                                                                                                   | Computer Networks Design and Management - 52                                                                              |  |  |  |

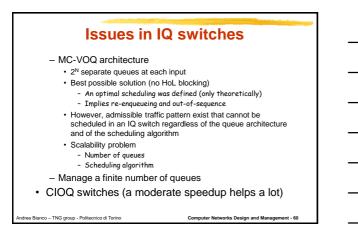

#### **Issues in IQ switches**

- · Signalling:

- Signalling bandwidth required to transfer weights from inputs to the controller may be significant with respect to the available bandwidth in the switching fabric

- The more complex the adopted metric, the larger the signalling bandwidth required

- Differential signalling may be adopted

- Multiple classes:

- Given K classes, first the VOQ architecture must be extended, by using KN queues at each input

- Scheduling algorithms must be extended to support priorities

Computer Networks Design and Mar

drea Bianco – TNG group - Politecnico di Torino

#### **Issues in IQ switches**

- · QoS (fair queueing)

- Scheduling for QoS (need to serve the most urgent packet) has a difficult interaction with the scheduling to transfer data from inputs to outputs

- Need to balance performance and fairness

- No ideal optimal solution known

- Frame scheduling

- Operate on a frame of length F slot, and compute a schedule on the frame and not on a slot by slot basis

- Scheduling algorithm executes only at frame boundaries

- Relatively easy to provide QoS guarantees for each input-output pair

- Delay increases at low loads

ndrea Bianco – TNG group - Politecnico di Torino

outer Networks Design and Managem

#### Issues in IQ switches

· Variable packet length support

May introduce packet scheduling instead of cell scheduling

· Packets transferred as trains of cells

- An edge is selected when the first cell of a packet arrives and is kept in all the following matchings until the last cell of the packet is transferred

- It avoids reassembly machines at outputs

- Same throughput guarantees

- Packet delay may be larger or shorter

Depends on packet length distribution

2 opende en pacitet lengin alet

a Bianco – TNG group - Politecnico di Torino

Computer Networks Design and Management - 5

# **Issues in IQ switches**

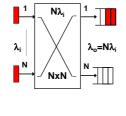

- · Multicast:

- 2<sup>N</sup> possible different multicast flows

- May be treated as unicast through input port replication (often named multicopy)

At each input a number of copies equal to the packet fanout are created, for the proper outputs, and inserted in the proper VOQ

- - Speedby required

Increases the instantaneous input load

May lead to low throuhgput (unable to sustain a single broadcast flow)

- Scheduling for multicast must be defined to exploit

switching fabric multicast capabilities

Balance fanout splitting and no-fanout splitting

Often a single FIPO for multicast is proposed (HoL blocking, less

critical with respect to unicast)

Original traffic

Computer Networks Design and Manag

ant - 58

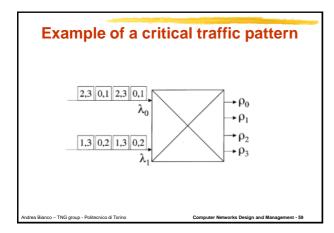

- · Critical traffic patterns when few inputs are active

a Bianco – TNG group - Politecnico di Torino

#### References

- Karok M, Huchyl M, Morgan S., "Input versus output queueing on a space division switch", IEEE Transactions on Communications, vol.35, n.12, Dec. 1997.

MicKown M, Asamtasam V, Walano JJ, "Achieving 100% throughput in an input-queued switch", IEEE Transactions on Meximum V, n.2, Apr. 1996, p.188-201

Tam Y, DH L-C, "Symmetric constate arbites for VLSI communications witches", IEEE Transactions on Pavalle and Dustrituted Systems, vol.4,

Advectore M, "Substance J, "Symmetric constate arbites for VLSI communication witches", IEEE Transactions on Pavalle and Dustrituted Systems, vol.4,

Advectore M, Substance J, Save J, Tabek C, "High peed switch scheduling for local area networks," ACM Transactions on Computer Systems, vol.4,

Advectore M, Substance JD, C., "Two dimensional cond-robot schedulers to placed avalles input queues", IEEE Transactions on Computer Systems, vol.1,

Advectore M, Substance JD, W, Two dimensional cond-robot schedulers to placed avalles input queues", IEEE Transactions on Computer Systems, vol.1,

Advectore M, Substance JD, W, Two dimensional cond-robot schedulers to placed avalles input queues fileEE/ACM Transactions on

Hordocommunications, vol.47, n.12, Berg DA, Bubba Amino, CD,

Morco Marana M, Bano A, Calccocone D, Leonard B, Leon MP, "Packet scheduling in prud-queued cell-based switches", IEEE Transactions on

Morco Marana M, Bano A, Calccocone D, Leonard B, Leon MF, "Packet scheduling in prud-queued cell-based switches", IEEE Transactions on

Morco Marana M, Bano A, Calccocone D, Leonard B, Leonard B, Leonard B, Leonard B, Leonard B, Leonard B, Leonard D, Leonard B, Leonard B Kim CK, Lee TT., "Call scheduling algorithm in multicast withching systems", IEEE Transactions on Communications, vol.40, n. 31, Mar. 1992, pp. 625-Philphaker B, McKevn N, Ankig R., "Multicast scheduling for input-queued awitches", IEEE Journal on Selected Ansas in Communications, vol.15, n.S. An. 1997, pp. 855-868 Andrews M, Starons S, Konzyan X, "Integrated scheduling of unclast and multicast stratilic in an input-queued awitch", IEEE MCOM 99, vol.31, Mar. 1992 Migrater R., "Scheduling multicast input-queued switches", Journal of Scheduling, John Willy & Son, May 1999 Algorine Marsan M, Biano A, Giaccone, Leonard E, Nen F, "On the throughput of Input-queued devices and saturbater tratter," IEEE INFOCOM 1, Archinge Ataka, Apr. 2007 I

- Computer Networks Design and Management 61

Irea Bianco – TNG group - Politecnico di Torino